- 您现在的位置:买卖IC网 > Sheet目录511 > SI5040-D-GM (Silicon Laboratories Inc)IC TXRX XFP 10GBPS 32LGA

�� �

�

Si5040�

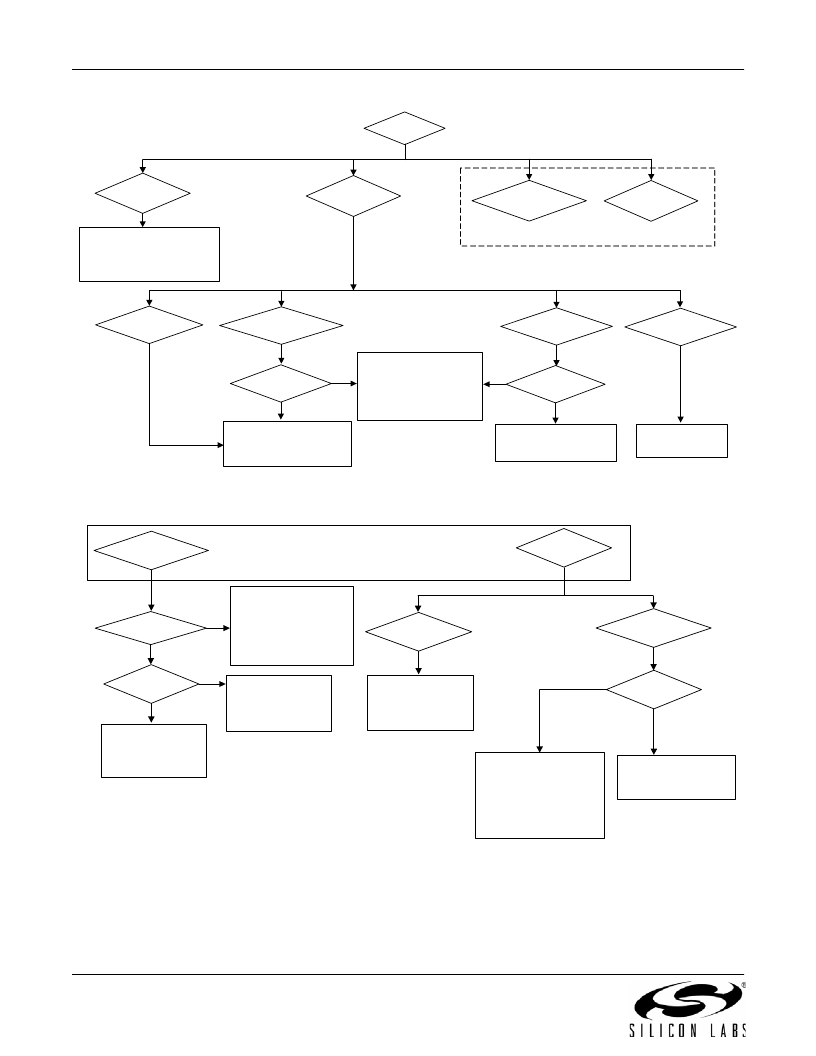

�LOS=1?�

�Y�

�Y�

�LOLonLOS� =0� and�

�ltrOnLos=0?� (Default)�

�LOLonLOS� =1�

�and� ltrOnLos� =0?�

�LOLonLOS� =� 0�

�and� ltrOnLos� =� 1?�

�LOLonLOS� =� 1�

�and� ltrOnLos� =� 1?�

�Y�

�CDR� continuously� tries� to� lock� to�

�incoming� data,� and� the� VCO�

�frequency� does� not� get� re-centered�

�prior� to� the� lock� acquisition�

�process.�

�Y�

�Next� Figure�

�VCOCAL[1:0]� =� 01?�

�VCOCAL[1:0]� =� 00?�

�VCOCAL[1:0]� =� 10�

�(Default)?�

�VCOCAL[1:0]� =� 11?�

�Y�

�Y�

�The� internal� VCO� pull�

�Y�

�Y�

�Is� refClk�

�present?�

�Y�

�range� will� be� automatically�

�re-centered� to� the�

�reference� clock� frequency�

�Y�

�Is� refClk�

�present?�

�to� start� the� CDR� lock�

�N�

�acquisition� process.�

�N�

�The� entire� VCO� frequency�

�range� will� be� swiped� to� start� the�

�CDR� lock� acquisition� process.�

�VCO� stays� at� the� center� of� its�

�frequency� range� awaiting� for�

�refClk.�

�Invalid� mode!�

�LOL� will� stay� on.�

�Figure� 12.� CDR� and� VCO� Behaviors� Upon� Declaring� LOS� (1� of� 2)�

�LOLonLOS� =� 0� and�

�ltrOnLos� =� 1?�

�Y�

�From� Previous� Figure�

�Since� ltr� has� been� set� to� 1�

�prior� to� the� assertion� of�

�LOLonLOS� =1� and�

�ltrOnLos� =1?�

�Y�

�Ltr� (bit� 1� in� Register� 7)=� 1?�

�Y�

�LOS,� CMU� maintains� lock�

�to� the� reference� and� the�

�CDR� lock� acquisition�

�VCOCAL[1:0]� =� X1?�

�VCOCAL[1:0]� =� X0?�

�depends� on� CDRLTDATA�

�N�

�control� in� Register� 7.�

�Y�

�Y�

�Is� refClk�

�present?�

�N�

�Y�

�CMU� locks� to� the�

�reference� clock� until�

�LOS� is� clear.� Note� that�

�LOL� will� be� off� during�

�this� period.�

�Invalid� mode!�

�ltrOnLOS� is� enabled�

�but� refClk� is� disabled.�

�Y�

�Is� refClk�

�present?�

�N�

�VCO� stays� at� the�

�center� of� its�

�frequency� range�

�awaiting� for� refClk.�

�The� internal� VCO� pull� range�

�will� be� automatically� re-�

�centered� to� the� reference�

�clock� frequency� to� start� the�

�VCO� stays� at� the� center� of�

�its� frequency� range� awaiting�

�for� refClk.�

�CDR� lock� acquisition�

�process.� Note� that� LOL� will�

�not� be� cleared.�

�Figure� 13.� CDR� and� VCO� Behaviors� Upon� Declaring� LOS� (2� of� 2)�

�22�

�Rev.� 1.3�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SI5402DC-T1-GE3

MOSFET N-CH D-S 30V 1206-8

SI5403DC-T1-GE3

MOSFET P-CH 30V 6A 1206-8

SI5432DC-T1-GE3

MOSFET N-CH 20V 6A 1206-8

SI5440DC-T1-GE3

MOSFET N-CH D-S 30V 1206-8

SI5441DC-T1-GE3

MOSFET P-CH D-S 20V 1206-8

SI5443DC-T1-GE3

MOSFET P-CH D-S 20V 1206-8

SI5468DC-T1-GE3

MOSFET N-CH D-S 30V 1206-8

SI5475BDC-T1-GE3

MOSFET P-CH 12V 6A 1206-8

相关代理商/技术参数

SI5040-D-GMR

制造商:Silicon Laboratories Inc 功能描述:XFP Transceiver 1TX 1RX 10Gbps 32-Pin LGA T/R 制造商:Silicon Laboratories Inc 功能描述:XFP TRANSCEIVER, PB FREE - Tape and Reel 制造商:Silicon Laboratories Inc 功能描述:IC TXRX XFP 10GBPS 32LGA

SI5040-D-ZM2

制造商:Silicon Laboratories Inc 功能描述:XFP TRANSCEIVER, PB FREE - Rail/Tube

SI5040-D-ZM6

制造商:Silicon Laboratories Inc 功能描述:XFP TRANSCEIVER - Rail/Tube

SI5040-D-ZM7

制造商:Silicon Laboratories Inc 功能描述:XFP TRANSCEIVER, PB FREE - Rail/Tube

SI5040-EVB

功能描述:BOARD EVAL SI5040 RoHS:否 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 主要目的:电源管理,电池充电器 嵌入式:否 已用 IC / 零件:MAX8903A 主要属性:1 芯锂离子电池 次要属性:状态 LED 已供物品:板

SI5041-B-GM

制造商:Silicon Laboratories Inc 功能描述:10G DUAL CDR (REV B FOR PROTOTYPE ONLY, REV C FOR P - Rail/Tube

SI5041-B-GMR

制造商:Silicon Laboratories Inc 功能描述:10G DUAL CDR (REV B FOR PROTOTYPE ONLY, REV C FOR P - Tape and Reel

SI5041-C-GM

制造商:Silicon Laboratories Inc 功能描述:10G DUAL CDR, LEAD FREE - Rail/Tube